PLL FM Detector

In an FM signal, the instantaneous frequency varies in accordance with the modulating signal. For a sinusoidal modulating signal, the frequency deviation in an FM signal is sinusoidal, and it is proportional to the modulating, amplitude. Recall that the changes in the instantaneous frequency of the carrier signal occur with respect to the previously attained value of the carrier frequency. This clearly suggests that a PLL can be used to demodulate an FM signal.

Suppose the center frequency of the FM signal is fc, and it lies within the hold-in range of PLL the VCO is locked to fc, by applying an demodulated carrier at the input of the phase detector. When VCO is locked to fc, the error signal is zero, and therefore, the control signal that changes the VCO frequency is also equal to zero. If an FM signal is applied to the phase detector, there will be a difference in the phases of the VCO output and the input FM signal. The control signal is produced in proportion to the phase difference at an instance of time. This control voltage will modify the VCO frequency, which is again compared with the incoming frequency. In this way, the current incoming frequency is compared with the previously attained value of the VCO frequency, which is the previously attained frequency of the FM Signal.

The VCO, therefore, tries to track the instantaneous frequency of the applied FM signal. The control signal is produced in proportion to the difference between the VCO frequency and the instantaneous frequency of FM signal. In other words, the control signal so produced is proportional to the frequency deviation in the FM signal. Since the frequency deviation si proportional to the modulating signal, the control signal appearing at the output of LPF is the modulating signal. Therefore, the FM signal is demodulated by PLL.

IC 565 PLL

A PLL is also available as an integrated circuit IC. IC 565 PLL can be used for FM detection.

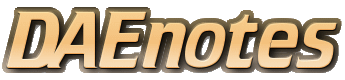

Figure (a) shows the circuit diagram of an FM detector using 565 PLL.

Internal Block Diagram of IC 565

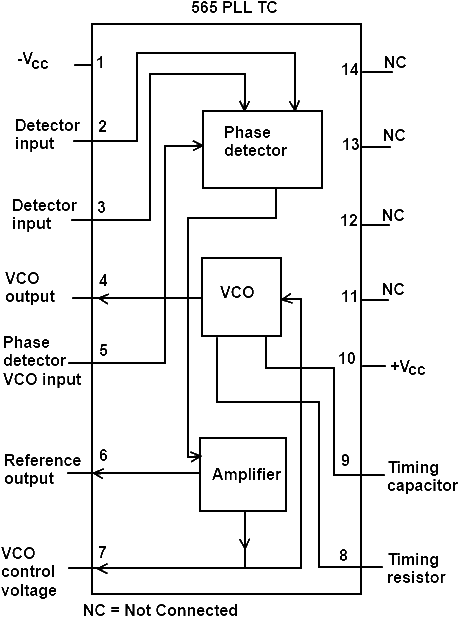

The internal block diagram shows that IC 565 PLL consists of phase detector, VCO, and amplifier. The amplifier also functions as the low pass filter. This is a 14 pin dual in line package.

In figure (b), notice that PLL IC consists of two power supply pins marked ±Vcc. The positive terminal of the Vcc is connected to pin number 10, and the negative (ground) terminal of Vcc is connected to pin number 1. The output signal to the phase detector is applied to pin numbers 2 and 3. The VCO output is applied to the phase detector through pin number 5. The output of the phase detector is internally connected to the amplifier (low-pass filter).

The output or the phase detector is low-pass filtered and amplified by the amplifier stage. The Output or the amplifier is the control voltage that is applied to VCO to force it to track the incoming frequency. The control voltage is also available at pin number 7. This is the output signal. In the ease of FM demodulator, the signal at pin number 7 is the modulating signal. The amplifier also generates an output at pin number 6for reference purposes.

The VCO gets its control voltage internally from the amplifier and its output at pin number 4. The VCO output should be given to the phase detector through pin number 5. It is customary to short pin numbers 4 and 5 so that the VCO output is applied directly to the phase detector. The external resistor and capacitor can set the free-running frequency of the VCO. The resistor and capacitor are called the timing resistor and the timing capacitor. The timing resistor is connected at pin number 8, and the timing capacitor is connected at pin number 9.

Pin numbers 11, 12, 13, and 14 are not connected because they do not have any internal circuitry with them. These are marked as NC in Figure (b). These pins are there because they are connected to IC.

Circuit Description

Figure (a) shows the circuit external to the IC 565 PLL for FM detection. The circuit shown in this figure is a general circuit. The choice of the timing components, resistor R0 and capacitor C0 decides the various parameters and the free-running frequency of PLL. Accordingly, the values of other components are also chosen.

In Figure (a), only a few components are externally connected to IC. The power supply, Vcc, is connected between pin numbers 1 and 10, with +Vcc applied at pin number 10. The timing resistor Ro is connected to pin number 8, and the timing capacitor, Co is connected to pin number 9. The VCO output, which is available at pin number 4 is applied to phase-detector input at pin number 5. Pin number 4 is shorted with pin number 5 as no external component is required in this case.

The input FM signal, Vi, is applied to pin number 2 through the coupling capacitor Cc. A part of this signal is also applied to pin number 3 through the potential divider network, consisting of R2, R3, and R4. The dc power supply is also provided to the input pins 2 and 3 through R1 from +Vcc supply. The capacitor C2 is used to filter out an AC ripple, if present in the DC supply.

The demodulated FM signal is nothing but the control signal, which is available at pin number 7. Therefore, the signal available at pin number 7 is the required modulating signal.

Parameters of Interest

The manufacturers of IC chips provide information related to the design of the circuit using their IC chips. They provide the design equations for important and key parameters of the circuit in terms of the circuit components and known circuit Conditions.

Some typical design equations for various parameters related to PLL operation are:

- Free-running frequency (fo). The free-running frequency of VCO may he calculated as:

f0 = 0.3/R0C0

For C0 = 1.5 nF and R0 = 20 KΩ, the free-running frequency is calculated as:

f0 = 0.3/(20 X 103)(1.5 X 10-9)

f0 = 10 KHz

Thus, for the central frequency of an FM signal to be 10 kHz, a resistor 420 KΩ and a capacitor of 1.5 nF can be used as timing components.

- Loop gain

The loop gain of PLL decides the amount of phase change among the input signals of the phase detector for a change in the input signal frequency. The loop may be defined as:

AL = KDKO per second

where

KD = Phase detector sensitivity in volt/radians

KO = Oscillator sensitivity in radians/see-volt

A typical formula given by a manufacturer nay be given is:

KDKO = 33.6 f0/Vc

Where

f0 = free-running frequency of Vco in Hz

Vc = Supply voltage

if Vc = 12 V and f = 10 KHz

KDKO = 33.6 X 10 X 103 f0/12

KDKO = 28 X 103

Therefore, the loop given for the given values of Vc and f0 is 28,000.

- Hold-in range

The hold-in range may be calculated as:

fh = ±8f0/Vc

Where

f0 = free running of VCO

Vc = supply voltage

For f0 = 10 KHz and Vc = 12 V, the hold-in range is calculated from above Equation as:

fh = ±8 X 10 X 103/12

fh = ±6.67 KHz

Therefore, for the given values, the loop will remain locked over a frequency range of ±6.67 KHz after it is locked initially.