Shift Registers

A register is a device which is used to store information. Flip flops are often used to make a register. Each flip flop can store 1-bit of information and therefore for storing a n-bit word n-flip-flops are required in the register for example a computer employing 16-bit word length requires 16 flip-flops to hold the number before it is manipulated. The input to a register or output from it may be either in serial or parallel form depending upon the requirement.

Shift Register

A shift register is a storage device that used to store binary data. When a number of flip flop are connected in series it is called a register. A single flip flop is supposed to stay in one of the two stable states 1 or 0 or in other words the flip flop contains a number 1 or 0 depending upon the state in which it is. A register will thus contain a series of bits which can be termed as a word or a byte.

If in these registers the connection is done in such a way that the output of one of the flip flop forms in input to other, it is known as a shift register. The data in a shift register is moved serially (one bit at a time).

The shift register can be built using RS, JK or D flip-flops various types of shift registers are available some of them are given as under.

- Shift Left Register

- Shift Right Register

- Shift Around Register

- Bi-directional Shift Register

Shift Left Register

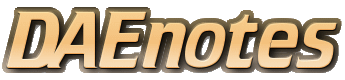

A four stage shift-left register is shown in figure 1. The individual stages are JK flip-flops. Notice that the date input consists of opposite binary signals, the reference data signal going to the J input and the opposite data signal going to the K input. For the D-type stage the single data input line is connected as the D-input.

The shift pulse is applied to each stage operating each simultaneously. When the shift pulse occurs the data input is shifted in to that stage. Each stage is set or reset corresponding to the input data at the time the shift pulse occurs. Thus the input data bit is shift in to stage A by the first shift pulse. At the same time the data of stage A is shifted into the stage B and so on for the following stages. At each shift pulse data stored in the register stages shifts left by one stage. New data shifted into stage A, whereas the data present in stage D is shifted out to the left for use by some other shift register or computer unit.

For example consider starting with all stages reset all Q-outputs to logical 0 and applying steady logical 1 input as data input stage A. Table 1 shows the data in each stage after each of four shift pulses. Notice table 2 how the logical 1 input first shifts into stage A and then left to stage D after four shift pulses.

As another example consider shifting alternate 0 and 1 data into stage A starting with all stages 1. Table 2 shows the data in each stage after each of four shift pulses.

Finally as a third example of shift register operation. Consider starting with the count in step 4 of table 2 and applying four more shift pulses with placing a steady logical 0 input as data input to stage A table 3 show this operation.

| Table 1 | ||||

|---|---|---|---|---|

| OPERATION OF SHIFT-LEFT REGISTER | ||||

| Shift Pulse | D | C | B | A |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 1 | 1 |

| 4 | 1 | 1 | 1 | 1 |

| Table 2 | ||||

|---|---|---|---|---|

| OPERATION OF SHIFT-LEFT REGISTER | ||||

| Shift Pulse | D | C | B | A |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 |

| 2 | 1 | 1 | 0 | 1 |

| 3 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 0 | 1 |

| Table 3 | ||||

|---|---|---|---|---|

| OPERATION OF SHIFT-LEFT REGISTER | ||||

| Shift Pulse | D | C | B | A |

| 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 1 | 0 | 0 | 0 |

| 4 | 0 | 1 | 0 | 0 |

Consider the data in stage A as least significant (2o) bits (LSB) and those in stage D as most significant bits MSB shift-left register operation provides data starting with MSB bit. A few points should be made clear in register operation.

- The number of shift pulses be the same as the number of shift in register stages.Consider the data in stage A as least significant (2o) bits (LSB) and those in stage D as most significant bits MSB shift-left register operation provides data starting with MSB bit. A few points should be made clear in register operation.

- Changes in the shift stages take place simultaneously but only the shift pulse occurs.

- Data shift into a register stage depends only on what logic levels were present at input terminals J and K at the time the shift pulse occurred. Changes that then take place resulting from data shifted will not affect the next stage until the next shift pulse occurs.

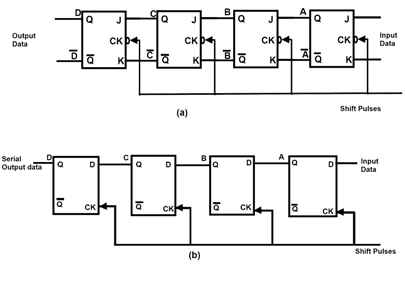

Shift Right Register

Sometimes it is necessary to shift the least significant digit first, as when addition is to be carried out serially. In that case a shift right register is used as in Figure 2 input data is applied to stage D and shifted right. The shift operation is the same as discussed in Shift Left Register except that data transfers to the right. Table 4 shows the action of shifting all logical 1 inputs into an initially reset shift register.

In addition to shifting data register, data into a register data is also of a register. Table 5 shows register operation for an initial value of 1101. Notice that the output from stage A contains the binary number each bit (starting initially with LSB) appearing at the output of each shift step. In the present example it was assumed that logical 0 was shifted as input data so that after four shift pulses have occurred the data has passed through the register and the stages are left reset after the fourth shift pulse.

| Table 4 | ||||

|---|---|---|---|---|

| SHIFT RIGHT OPERATION | ||||

| Shift Pulse | D | C | B | A |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 2 | 1 | 1 | 0 | 0 |

| 3 | 1 | 1 | 1 | 0 |

| 4 | 1 | 1 | 1 | 1 |

| Table 5 | ||||

|---|---|---|---|---|

| SHIFTED OUT OF SHIFT RIGHT REGISTER | ||||

| Shift Pulse | D | C | B | A |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 0 | 0 | 1 |

| 4 | 0 | 0 | 0 | 0 |

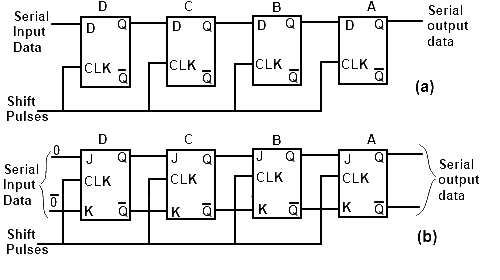

Shift Around Register

When it is required to shift data out of a register with out losing the initial data a shift around register can be used. Figure 3 shows the JK stages in a shift right, shift around register connection. All that was needed was connection of the input of stage A as into the stage D. Then as four shift pulses move the binary data into stage A, the data being shift out of stage A is shift into stage D and returns into the register.

| Table 6 | ||||

|---|---|---|---|---|

| AROUND ACTION WITH SHIFT RIGHT REGISTER | ||||

| Shift Pulse | D | C | B | A |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

| 2 | 0 | 1 | 1 | 1 |

| 3 | 1 | 0 | 1 | 1 |

| 4 | 1 | 1 | 0 | 1 |

Table 6 shows the result of shifting the binary number 1101 through (and around) the shift register.

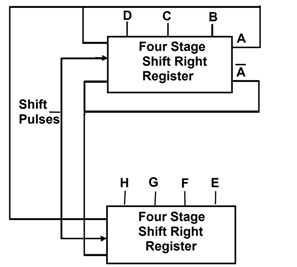

Notice that after four shift pulses have occurred the initial value is again in the shift register. To see how any action has taken place other than just shifting the number around there register consider tow shift register stages as in Figure 4 each register, shows in block form, is a four stage shift right register. Externally connecting the A and  output of register 1 back to the data input of the same register results in it acting as a shift around register. The logic signal appearing at output A and

output of register 1 back to the data input of the same register results in it acting as a shift around register. The logic signal appearing at output A and  is also shifted into register 2. Table 7 shows the operation of starting with 1101 in register 1 and 000 in register 2 if the shift around of register 1 were not used and data input were left uncommented (logical 0) then after four shift pulses the data originally in register 1 would be in register 2, with register 1 then reset.

is also shifted into register 2. Table 7 shows the operation of starting with 1101 in register 1 and 000 in register 2 if the shift around of register 1 were not used and data input were left uncommented (logical 0) then after four shift pulses the data originally in register 1 would be in register 2, with register 1 then reset.

| Table 7 | ||||||||

|---|---|---|---|---|---|---|---|---|

| OPERATION OF SHIFT REGISTERS OF FIGURE 4 | ||||||||

| Shift Pulse | D | C | B | A | H | G | F | E |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

| 2 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 3 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 4 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

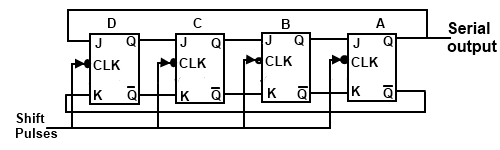

Bidirectional Shift Register

A bidirectional shift register is one which can do both the shift left and shift right operations. The arrangement is shown in Figure 5 there are two separate sets of flip-flops. The following steps are controlled by a clock sequentially. The clock and timing arrangements have not been shown in the figure. The lower register is the one in which the data being shifted right or left. The upper register is being used as a temporary storage. The steps are as follows.

- The contents of the lower register are gated up directly to the upper register, which is assumed to have been cleared previously. This is a parallel transfer of data and is achieved by the first pulse or gate up pulse applied as the gate up terminals.

- All the lower registers are reset i.e. set =0 by giving a pulse at the reset terminals.

- The contents of the upper register are gate down to the lower register either one position to the right or to the left as desired. This is again a parallel transfer of data.

- The upper register is reset for the next shift operation.

Asynchronous and Synchronous Shift Registers

Asynchronous circuits changes state each time the input changes the state, while synchronous circuit changes state only when triggered by a momentary change in the input signal. This momentary change is called triggering.

Shift registers are made of flip flops their operation depends upon the state at the flip flop and their operation depends upon the state at the flip flops. Flip flops changes their states due to triggering when flip flop change their state on the base of input pulse then it is called Edge triggering. In edge triggering flip flop change its state on the basses of Leading edge or trailing edge. When flip flop works on the bases of change in DC level, that is called Asynchronous Triggering. And the shift registers work on this principle are called Asynchronous shift registers. On the other hand, shift registers changes their state only when triggered by clock pulse are called Synchronous shift registers these type of shift registers usually used in counters.